- 您现在的位置:买卖IC网 > Sheet目录342 > MCBSTM32EXL (Keil)BOARD EVALUATION FOR STM32F103ZE

RM0008

Advanced-control timers (TIM1&TIM8)

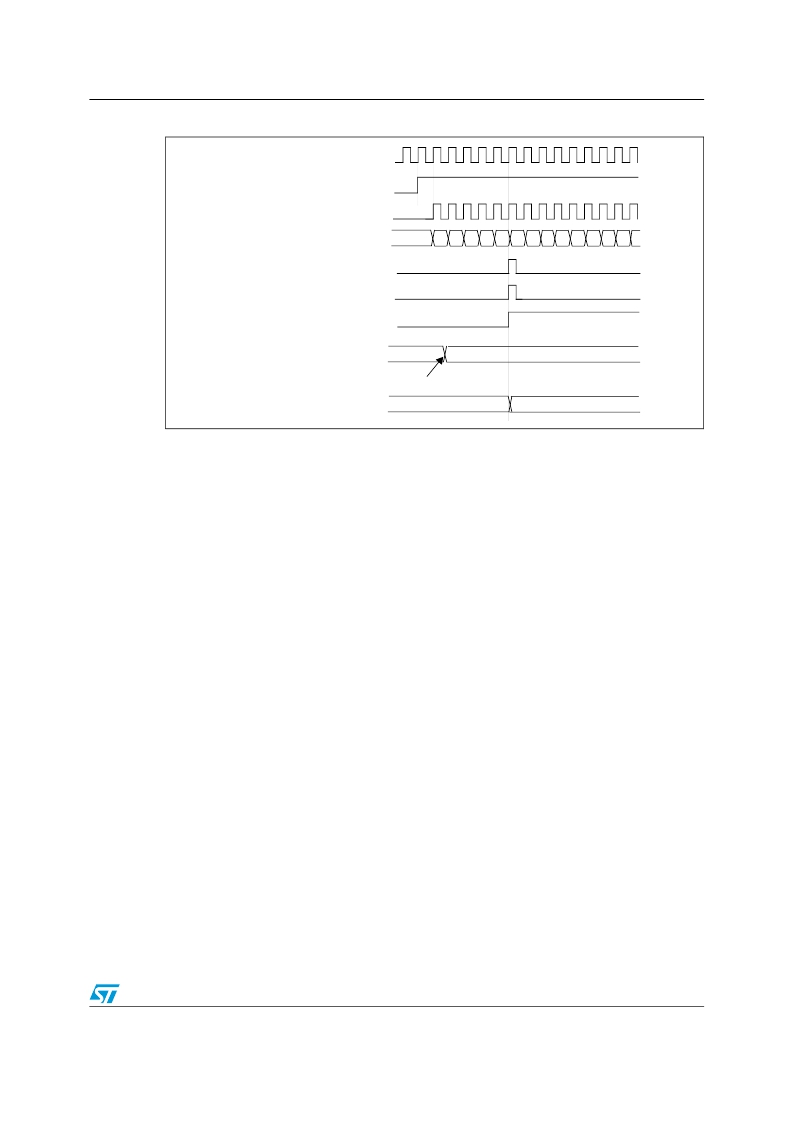

Figure 70. Counter timing diagram, Update event with ARPE=1 (counter overflow)

CK_PSC

CEN

Timer clock = CK_CNT

Counter register

Counter overflow

Update event (UEV)

Update interrupt flag (UIF)

Auto-reload preload register

F7

FD

F8 F9 FA FB F C 36 35 34 33 32 31 30 2F

36

Write a new value in TIMx_ARR

13.3.3

Auto-reload active register

Repetition counter

FD

36

respect to the counter overflows/underflows. It is actually generated only when the repetition

counter has reached zero. This can be useful when generating PWM signals.

This means that data are transferred from the preload registers to the shadow registers

(TIMx_ARR auto-reload register, TIMx_PSC prescaler register, but also TIMx_CCRx

capture/compare registers in compare mode) every N counter overflows or underflows,

where N is the value in the TIMx_RCR repetition counter register.

The repetition counter is decremented:

●

●

●

At each counter overflow in upcounting mode,

At each counter underflow in downcounting mode,

At each counter overflow and at each counter underflow in center-aligned mode.

Although this limits the maximum number of repetition to 128 PWM cycles, it makes it

possible to update the duty cycle twice per PWM period. When refreshing compare

registers only once per PWM period in center-aligned mode, maximum resolution is

2xT ck , due to the symmetry of the pattern.

The repetition counter is an auto-reload type; the repetition rate is maintained as defined by

the TIMx_RCR register value (refer to Figure 71 ). When the update event is generated by

software (by setting the UG bit in TIMx_EGR register) or by hardware through the slave

mode controller, it occurs immediately whatever the value of the repetition counter is and the

repetition counter is reloaded with the content of the TIMx_RCR register.

Doc ID 13902 Rev 9

265/995

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCBTMPM330

BOARD EVAL TOSHIBA TMPM330 SER

MCIMX25WPDKJ

KIT DEVELOPMENT WINCE IMX25

MCIMX53-START-R

KIT DEVELOPMENT I.MX53

MCM69C432TQ20

IC CAM 1MB 50MHZ 100LQFP

MCP1401T-E/OT

IC MOSFET DRVR INV 500MA SOT23-5

MCP1403T-E/MF

IC MOSFET DRIVER 4.5A DUAL 8DFN

MCP1406-E/SN

IC MOSFET DVR 6A 8SOIC

MCP14628T-E/MF

IC MOSFET DVR 2A SYNC BUCK 8-DFN

相关代理商/技术参数

MCBSTM32EXLU

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINK2 FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32EXLU-ED

制造商:ARM Ltd 功能描述:KEIL STM STM32EXL EVAL BOARD

MCBSTM32EXLUME

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINKME FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200U

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG + ULINK2

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG ULINK-ME

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME-ED

制造商:ARM Ltd 功能描述:KEIL STM32F207IG EVAL BOARD

MCBSTM32F400

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F407IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V